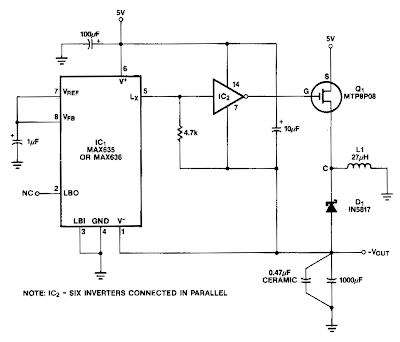

In this Medium Power Inverter Circuit Diagram, a CMOS inverter, such as the CD4069, is used to convert the open drain Lx output to a signal suitable for driving the gate of an external P MOSFET. The MTP8P03 has a gate threshold voltage of 2.0 V to 4.5 V, so it will have a relatively high resistance if driven with only 5 V of gate drive.

To increase the gate drive voltage, and thereby increase efficiency and power handling capability, the negative supply pin of the CMOS inverter is connected to the negative output, rather than to ground. Once the circuit is started, the P MOSFET gate drive swings from +5 V to -Vour· At start up, the -Vour is one Schottky diode drop above ground and the gate drive to the power MOSFET is slightly less than 5 V.

Medium Power Inverter Circuit Diagram

The output should be only lightly loaded to ensure start up, since the output power capability of the circuit is very low until -VoUT is a couple of vults. This circuit generates complementary output signals from 50 to 240 Hz. Digital timing control ensures a separation oflO to 15° between the fall time of one output and the rise time of the complementary output. The digital portion of inverter Ul to U4 controls the drive to Q1 and Q2, both MTE60N20 TMOS devices.

These devices are turned on alternately with 11.25° separation between complementary outputs. A +12-V supply for CMOS gates U1 to U4 is developed by T1, D3, D4, C7, and U6. The power supply for the TMOS frequency generator is derived from the diode bridge, U5, and capacitor C7; it is applied to the center tap of T2.

0 komentar:

Posting Komentar